¶ IP 核生成

¶ 1. IP 核创建

参考快速入门,创建名为 XCZU47DR_ADDS 的工程文件。

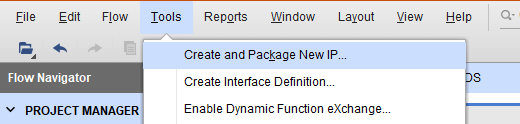

选择 Tool -> Create and Package New IP

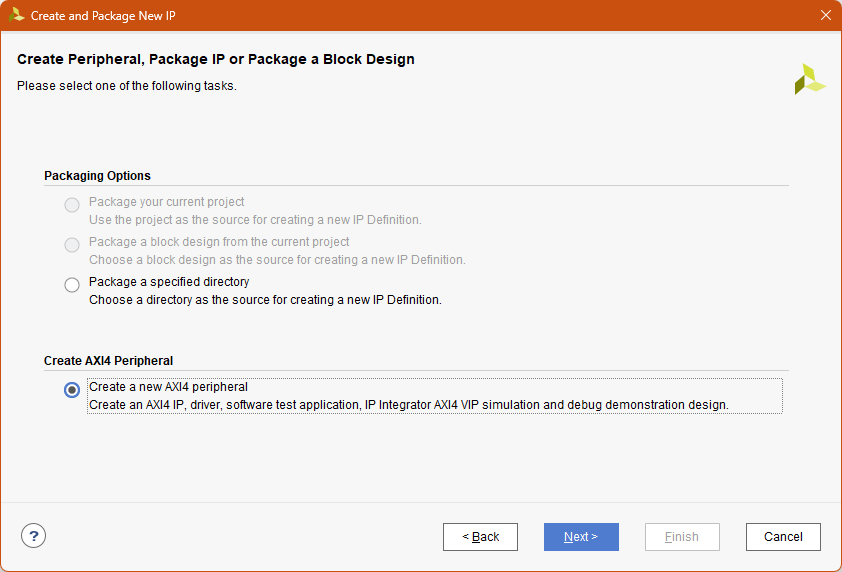

在本页面选择创建新的 AXI4 外设,它为 IP 核创建 makefile、驱动例程等。

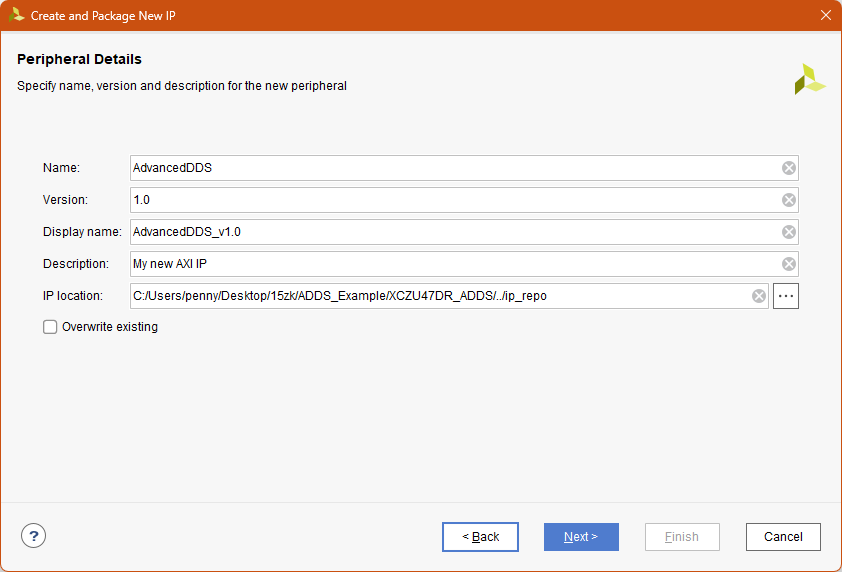

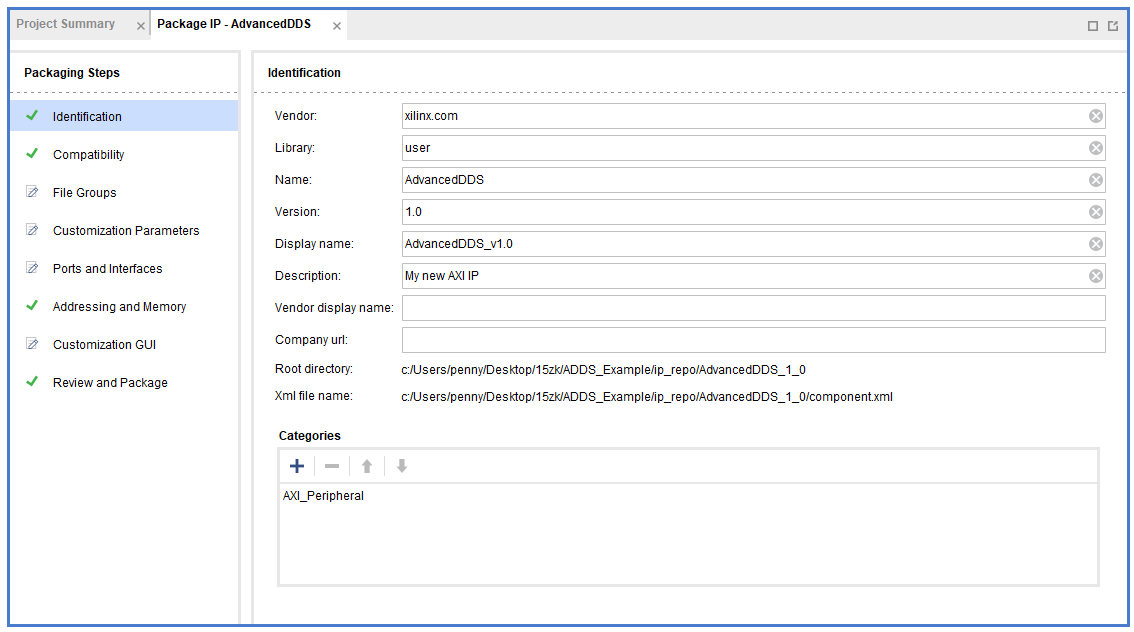

修改 ip 核名称

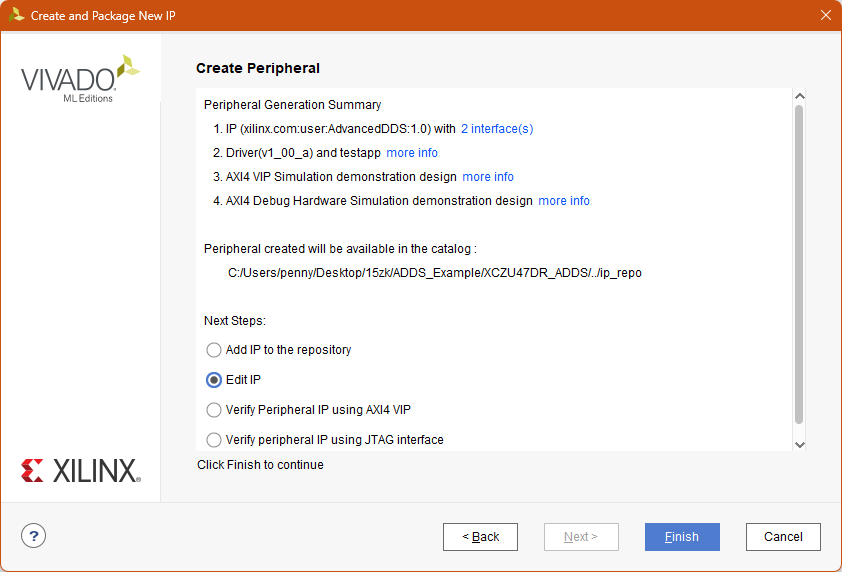

跳过添加接口,后面我们可以直接导入 Verilog 文件进行识别。

到最后一页,选择 edit IP,进入 IP 的编辑界面。

¶ 2. IP 核编辑

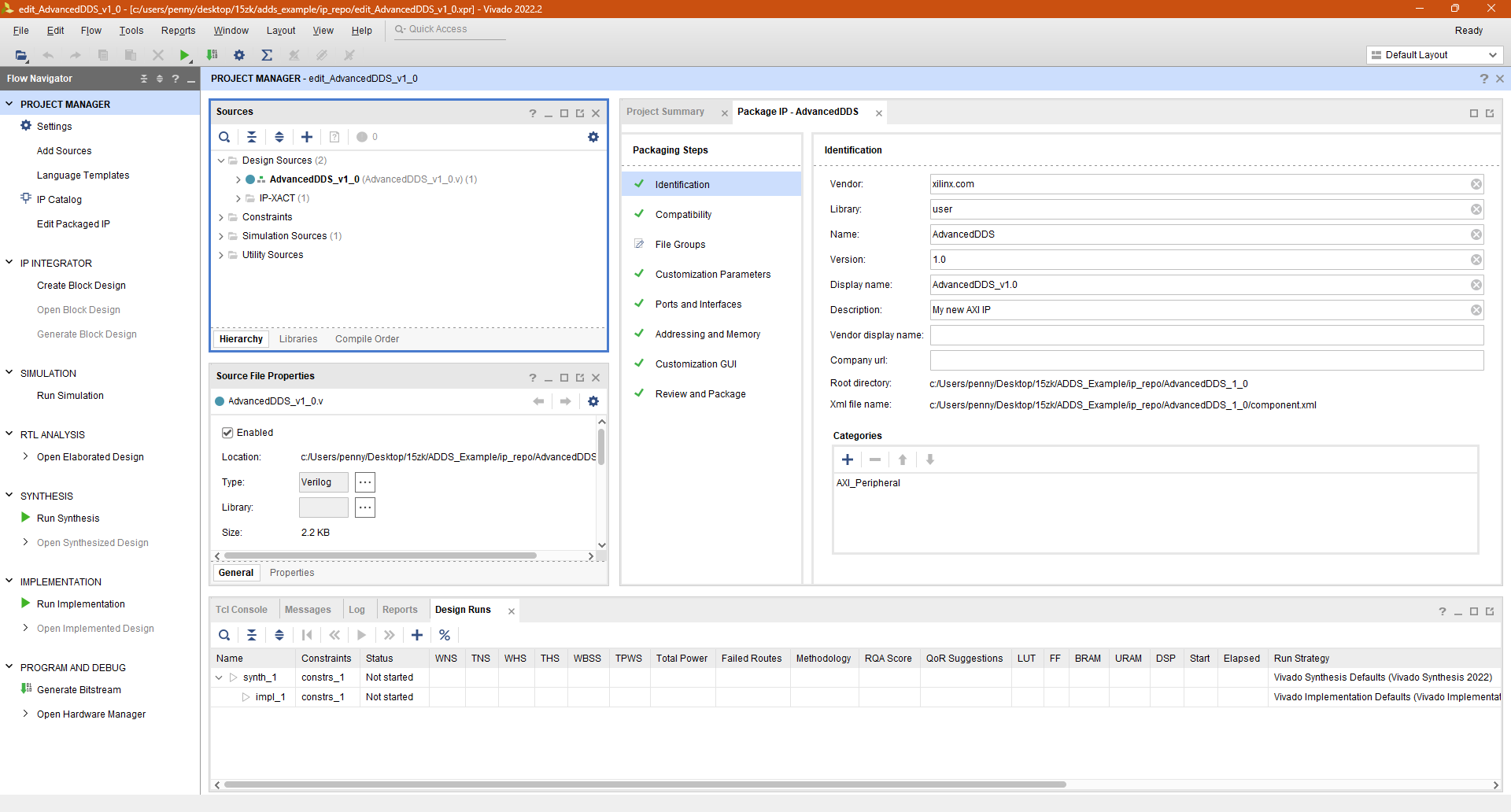

进入 IP 核编辑界面:

¶ 2.1. 修改 sources

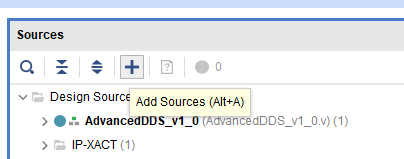

添加 sources

将运行 scala 脚本后生成的 verilog 文件添加进来,它在项目目录下的 output 文件夹中:

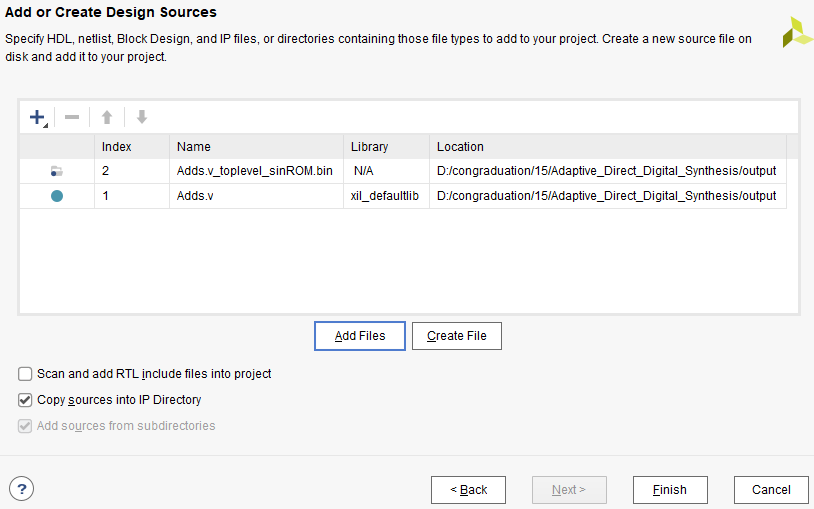

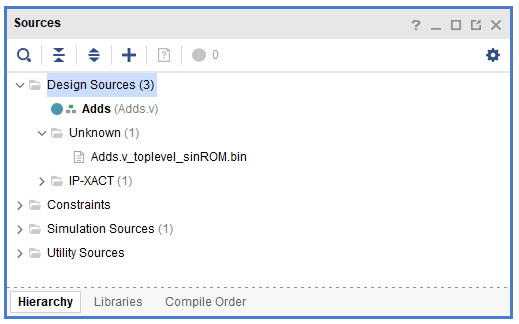

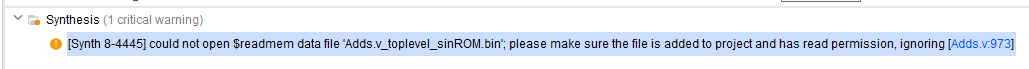

删除新建项目生成的示例 verilog 代码,将导入的 Adds 置为顶层。导入完成后此时项目中的 Sources 结构如图所示:

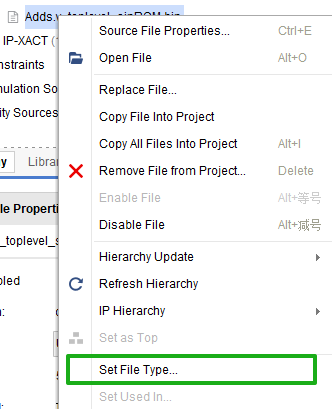

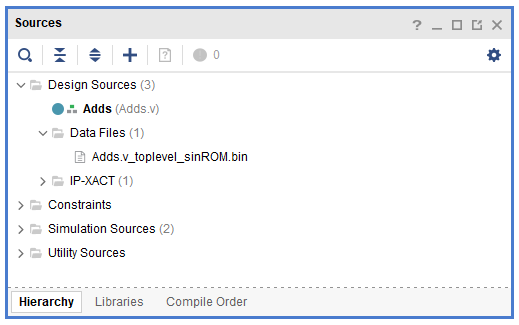

注意到新导入的 ROM 是 Unknown,我们需要右键点击它,手动修改文件类型为 Data Files:

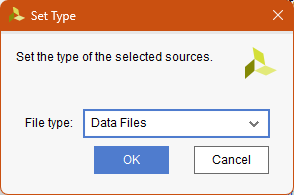

如果没有进行这一步,则. bin 文件不会用于综合,产生报错:

最终正确的 IP 和 Design Sources 结构为:

¶ 2.2. IP 核打包

接下来我们关注右边的 Package IP 窗口,完成打包步骤。

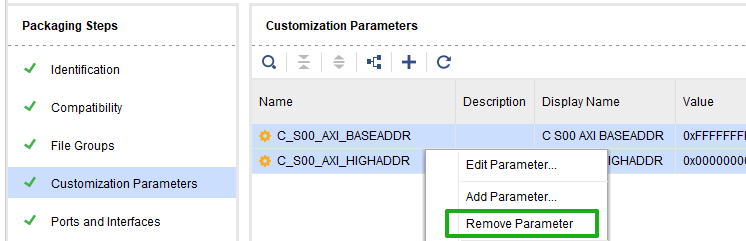

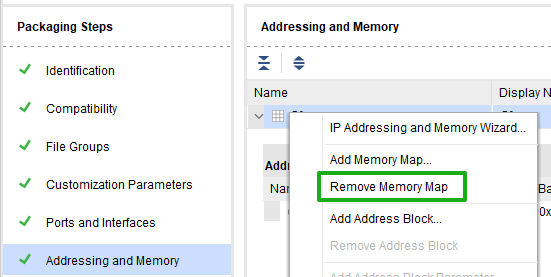

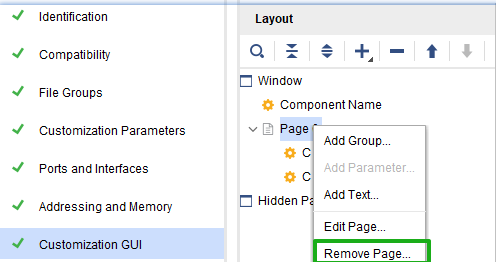

删除例程包含的 S00_AXI 的参数、地址和 GUI 参数配置页面:

有四个未完成项,这里可以直接选择 Merge changes from XXX 即可使用 vivado 的自动化工具完成。

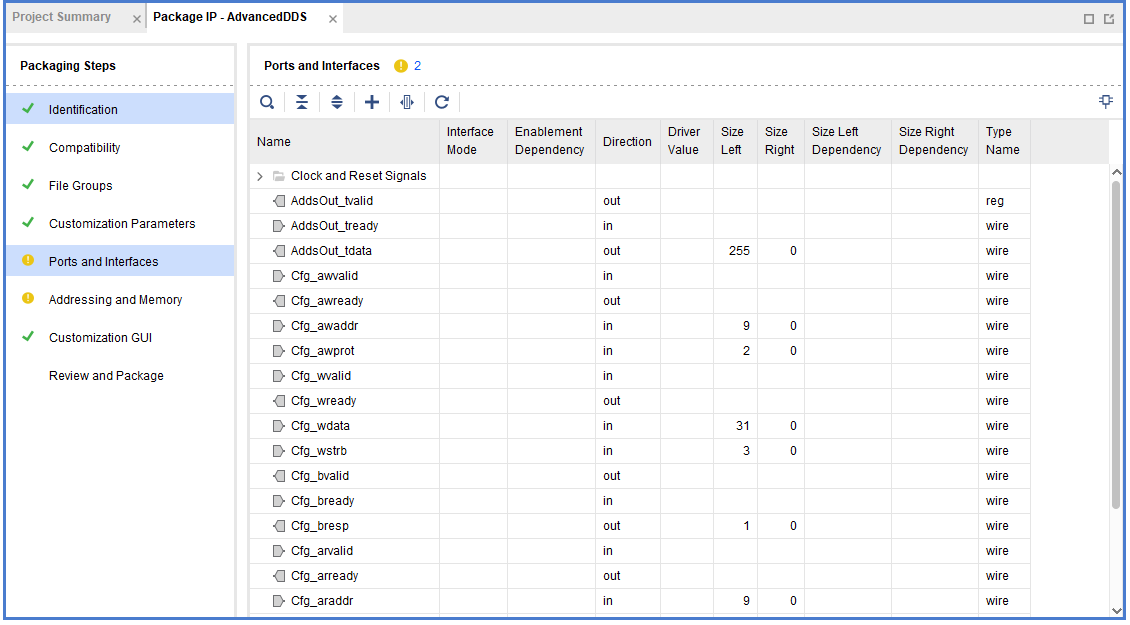

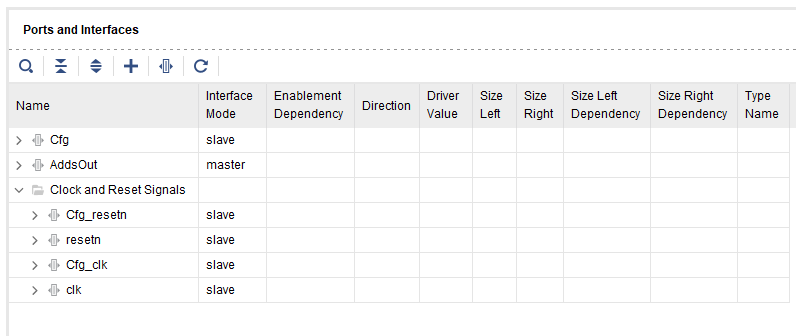

在 Ports and Interfaces 中出现报错:

这里我们使用 Auto Infer Interface

不选任何 Interface 直接让它自动识别:

检查线束识别是否正确,这里对应我们在 [[ADDS 手册) 中的接口定义。

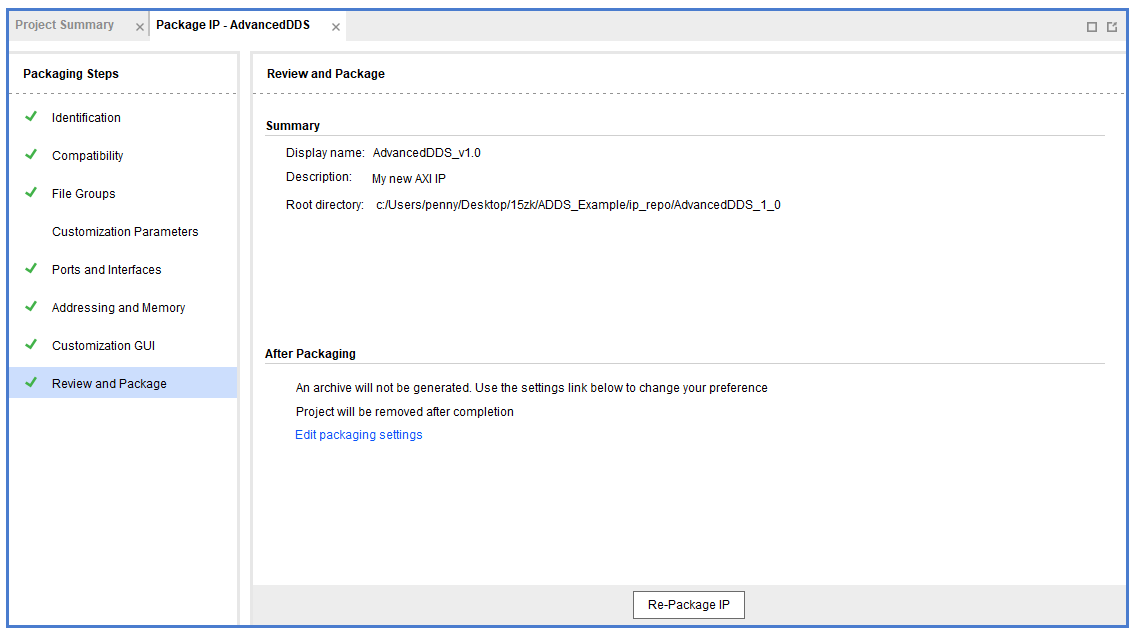

检查完成后,在 Review and Package 界面进行 IP 重打包

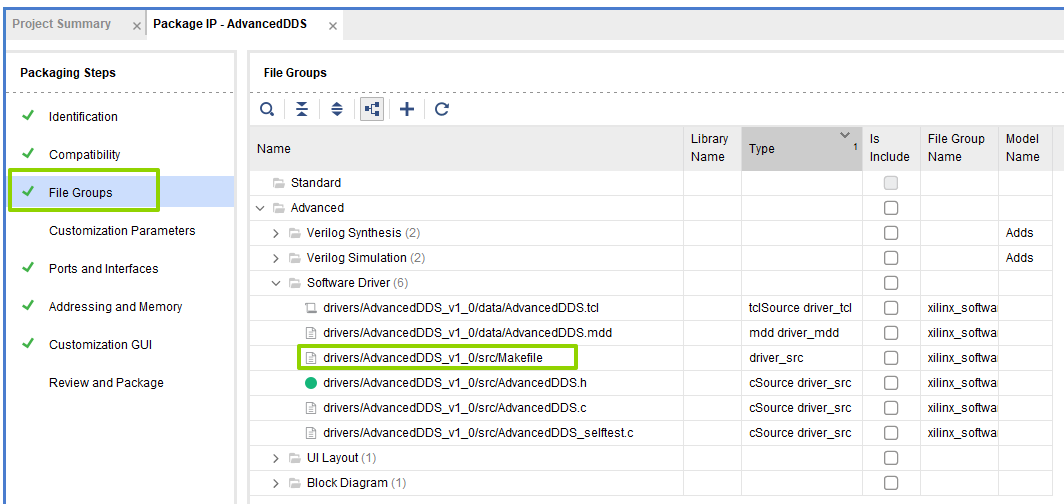

¶ 2.3 makefile 修改

请注意,为了避免 IP 核在 Vitis 中 makefile 报错,我们需要在 IP 核制作时将vivado自动生成的 makefile 替换成可以运行的 makefile。

在 File Groups 中找到 Makefile 文件,双击。

全选,将原有的 Makefile 文件替换为 Xilinx 其它 IP 核的通用 makefile:

DRIVER_LIB_VERSION = 1.0

COMPILER=

ARCHIVER=

CP=cp

COMPILER_FLAGS=

EXTRA_COMPILER_FLAGS=

LIB=libxil.a

CC_FLAGS = $(COMPILER_FLAGS)

ECC_FLAGS = $(EXTRA_COMPILER_FLAGS)

RELEASEDIR=../../../lib/

INCLUDEDIR=../../../include/

INCLUDES=-I./. -I$(INCLUDEDIR)

SRCFILES:=$(wildcard *.c)

OBJECTS = $(addprefix $(RELEASEDIR), $(addsuffix .o, $(basename $(wildcard *.c))))

libs: $(OBJECTS)

DEPFILES := $(SRCFILES:%.c=$(RELEASEDIR)%.d)

include $(wildcard $(DEPFILES))

include $(wildcard ../../../../dep.mk)

$(RELEASEDIR)%.o: %.c

${COMPILER} $(CC_FLAGS) $(ECC_FLAGS) $(INCLUDES) $(DEPENDENCY_FLAGS) $< -o $@

.PHONY: include

include: $(addprefix $(INCLUDEDIR),$(wildcard *.h))

$(INCLUDEDIR)%.h: %.h

$(CP) $< $@

clean:

rm -rf ${OBJECTS}

rm -rf $(DEPFILES)

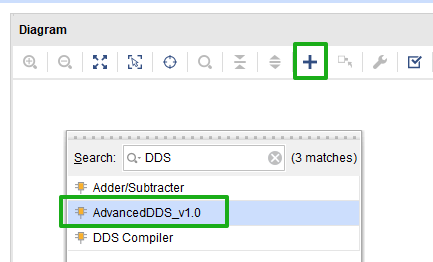

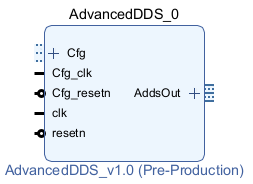

回到 XCZU47DR 后,创建 Block Design 后就可以点➕搜索添加我们刚创建的 IP 了。

¶ ZYNQ 配置

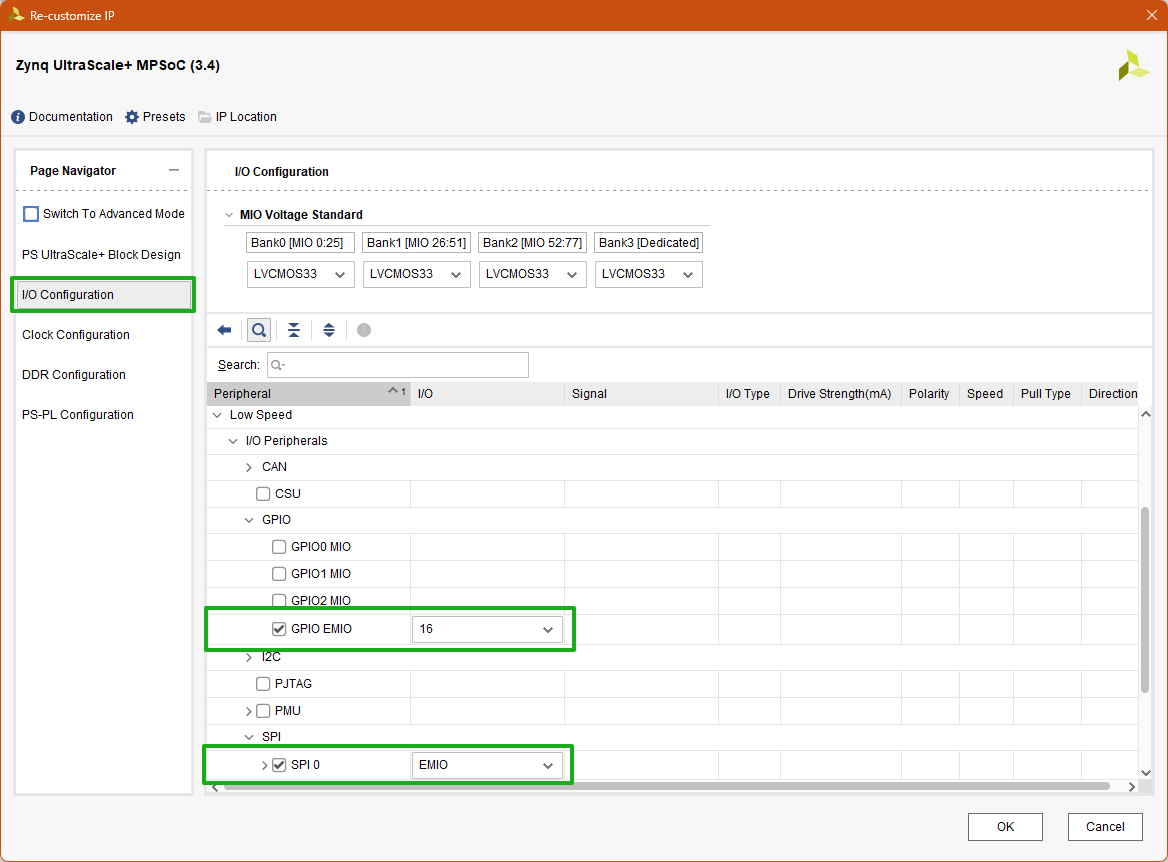

添加 ZYNQ UltraScale+ MPSoC ,双击模块配置对应的 SPI 、 GPIO:

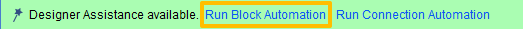

运行 Run Block Automation 和 Run Connection Automation,保持默认即可。

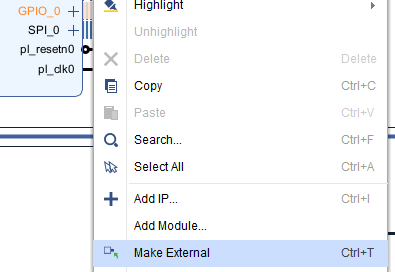

引出 GPIO 和 SPI,用于 LED 和 LMK SPI 通信。依次选中 GPIO_0 和 SPI_0 接口,右键选择 Make External,引出引脚。

¶ RFSoC 配置

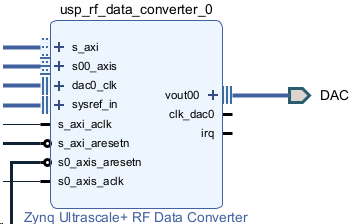

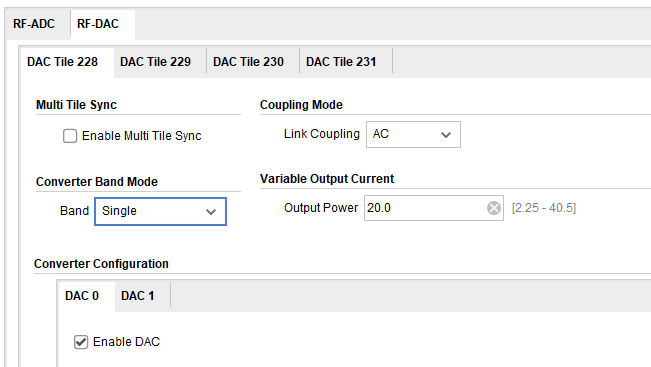

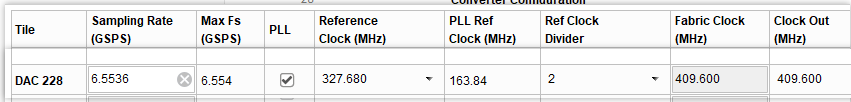

双击进入 RF Data Converter 配置

Sampling Rate: 6.5536 G SPS(每秒采样数)

Fabric Clock: 409 600 000

Reference Clock: 327 680 000 (配置在 LMK 驱动中,CLK_IN_REF)

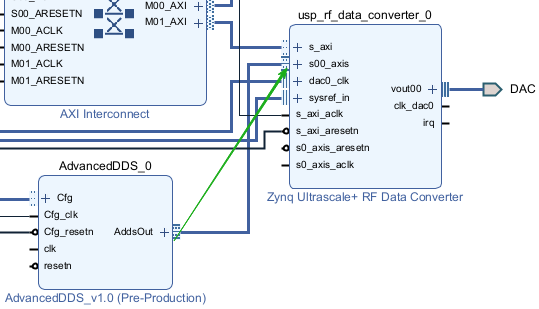

手动连接 ADDS 输出和 rf data converter 输入

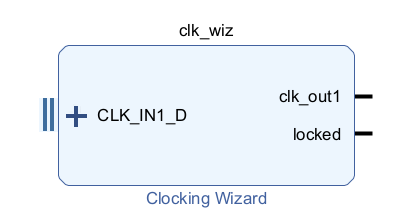

手动添加 Clocking Wizard:

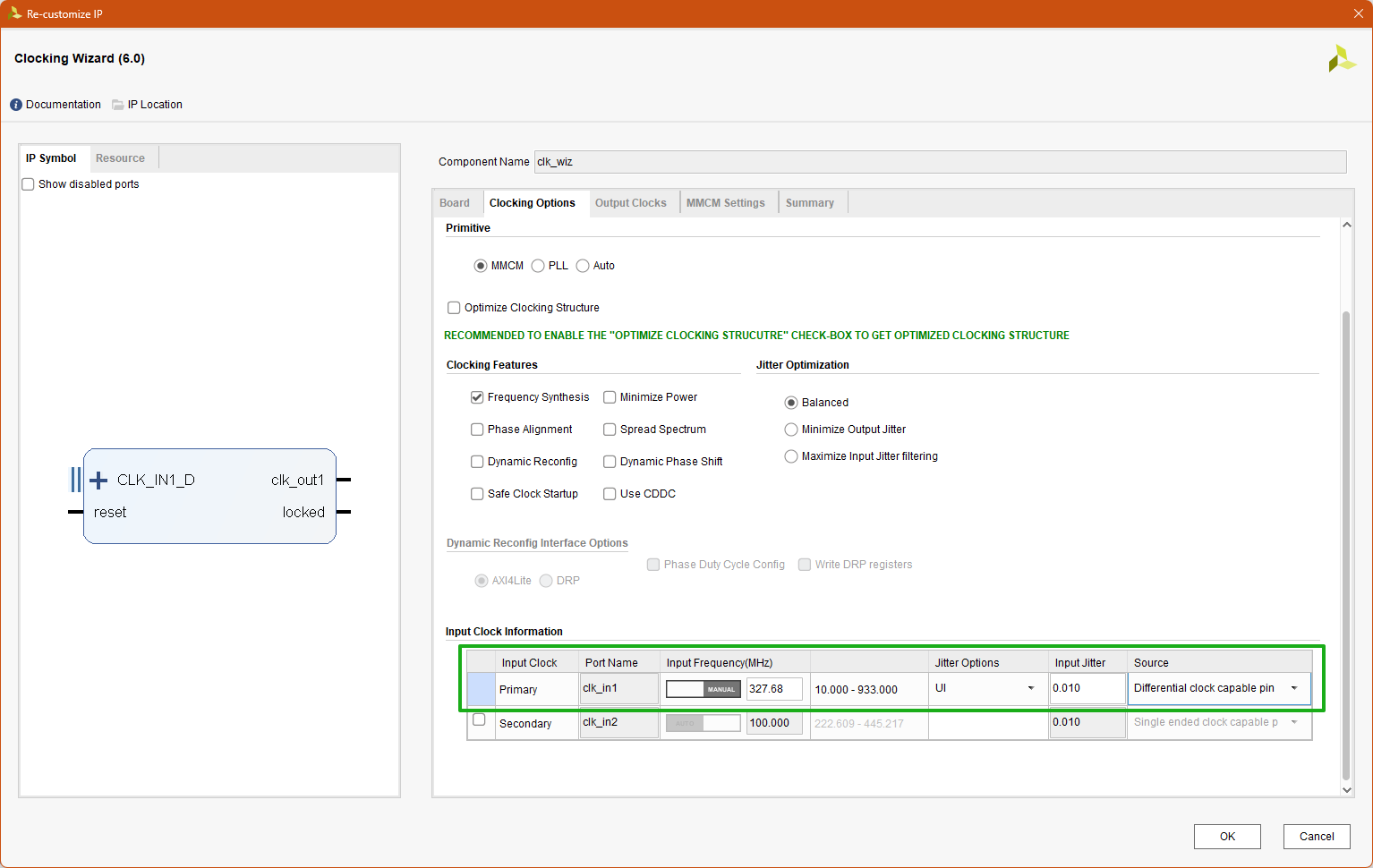

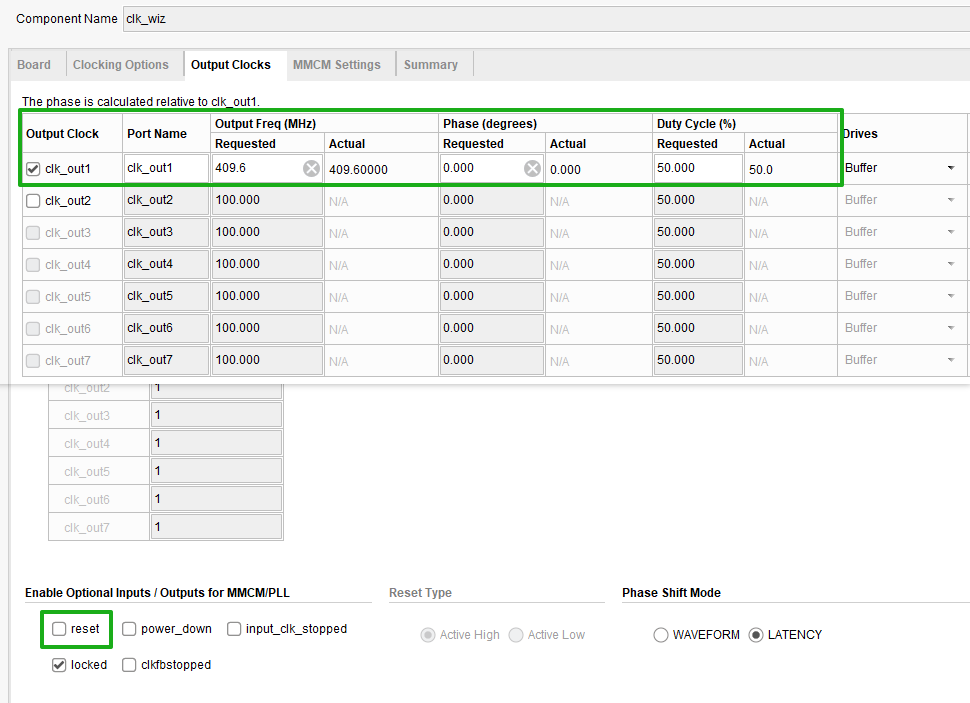

在 Clocking Options 页面修改输入时钟:

在 Output Clocks 页面修改输出频率,并且关闭输入 reset 引脚。

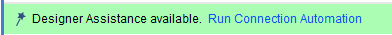

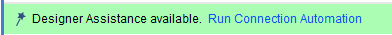

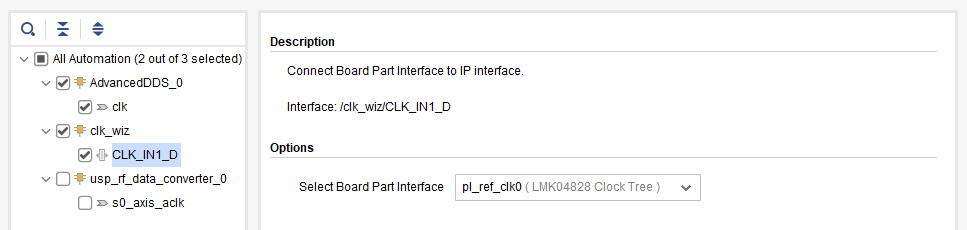

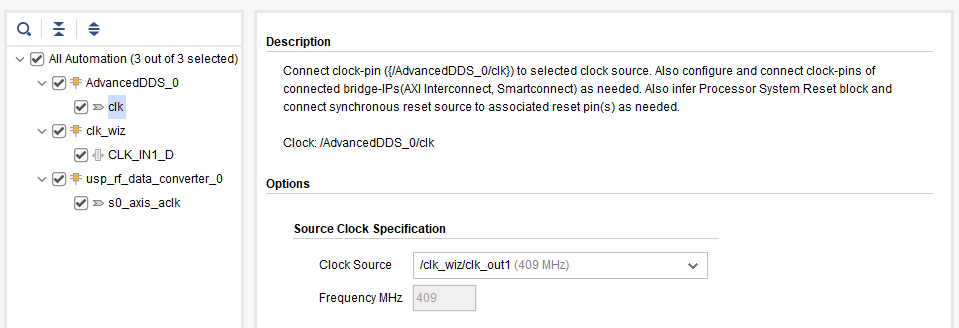

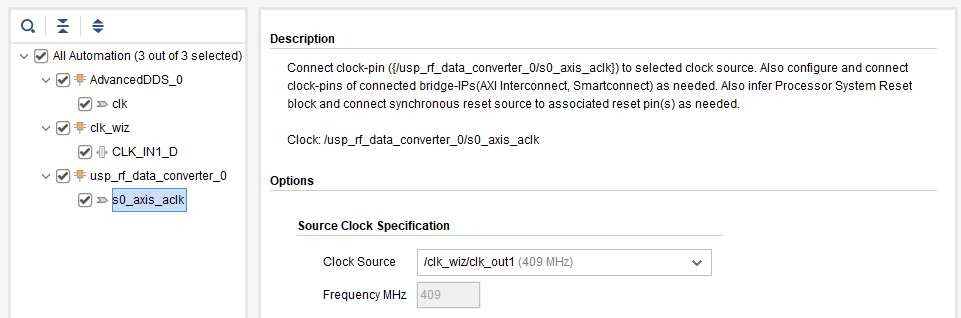

完成 clock 的配置之后,使用 Run Connection Automation 完成余下的配置:

将 pl_ref_clk0 给到 clk_wiz 输入,这个 pl_ref_clk0 是:

将 clk_wiz 输出给到 adds:

将 clk_wiz 输出给到 rf_data_converter

¶ 地址配置

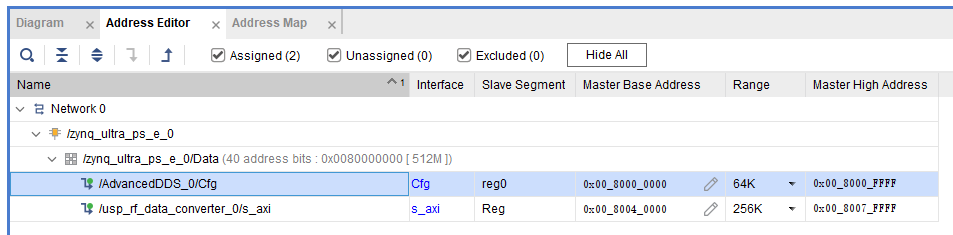

配置 AdvancedDDS 核 rd data converter 的寄存器地址:

¶ ila 配置

使用 ila 用于看我们设计 ADDS 的信号输出是否正确。

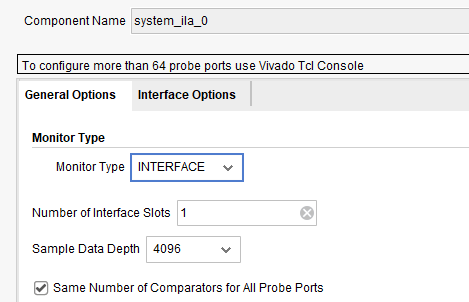

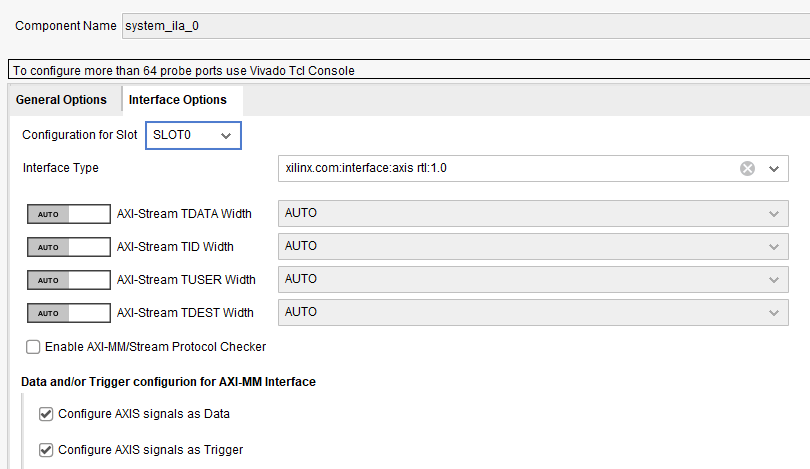

添加 ila,将深度改为4096:

接口改为 axis rtl

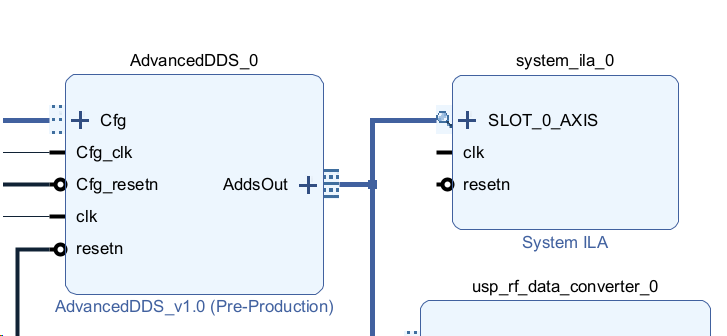

将 SLOT_0_AXIS 连接到 AddsOut,

运行 Run Connection Automation, 使用默认配置。

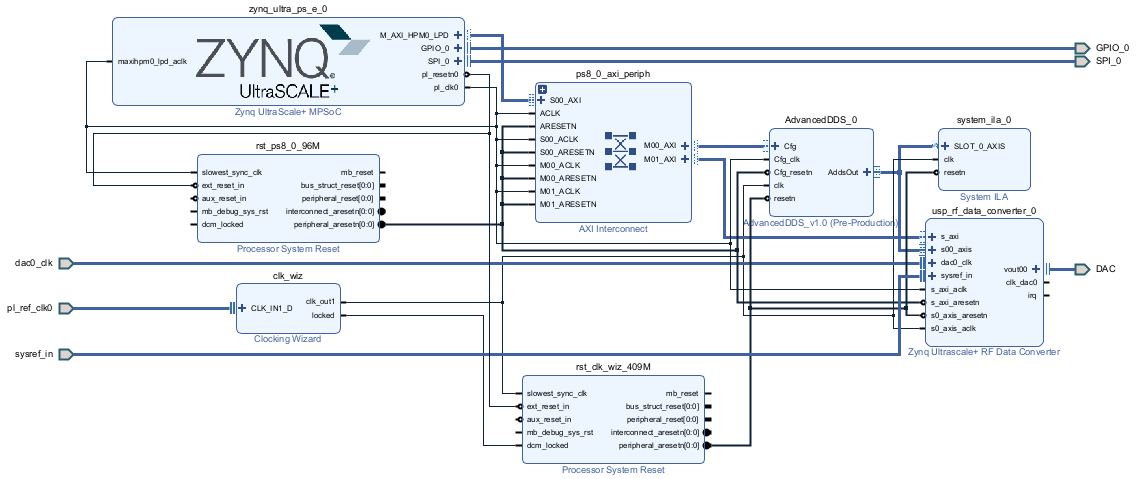

如果操作正确的话,最后的 Block Design 应该如下所示:

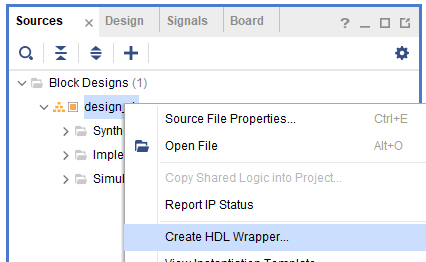

为创建的 Block Design 添加 HDL Wrapper:

如果所有设置都没有问题,即可以直接点击"Generate Bitstream"生成"BIT"文件。

¶ PS 端配置

¶ 1. 创建 Platform 工程

参考快速开始 ,导入 xsa 并创建 Platform 工程。

¶ 2. 创建 Application 工程

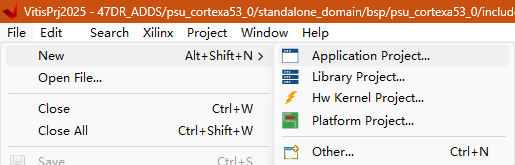

在导航栏选择 File-> New -> Application Project

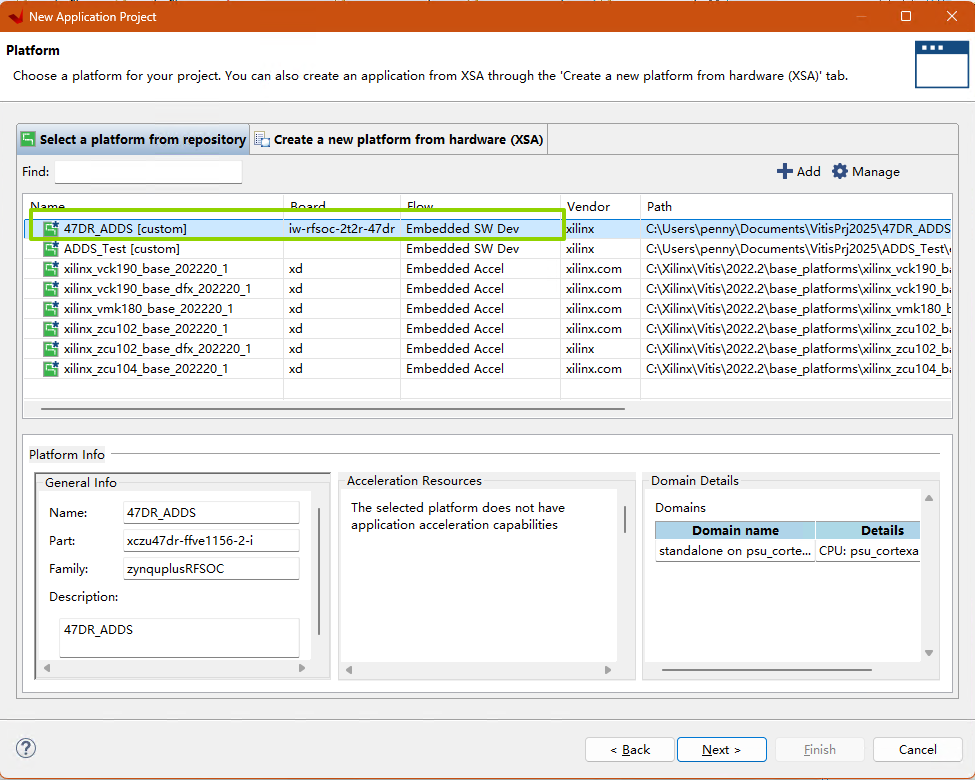

在 Platform 页面选择刚刚创建好的47DR_ADDS。

s

s

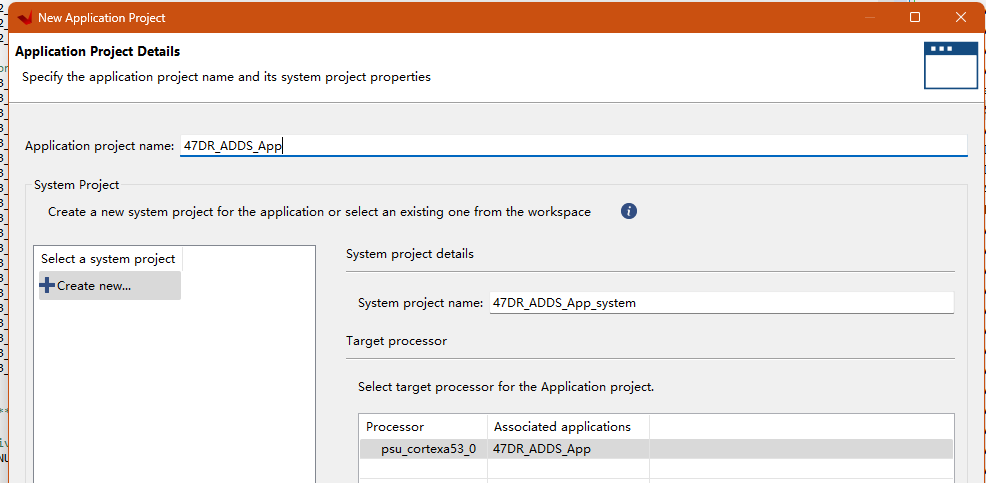

将新项目命名为47DR_ADDS_App,

其他步骤直接选择 Next,创建一个基于 HelloWorld 的工程。

¶ 2.1 添加 LMK 时钟驱动

下载并导入LMK04828 时钟PLL计算程序