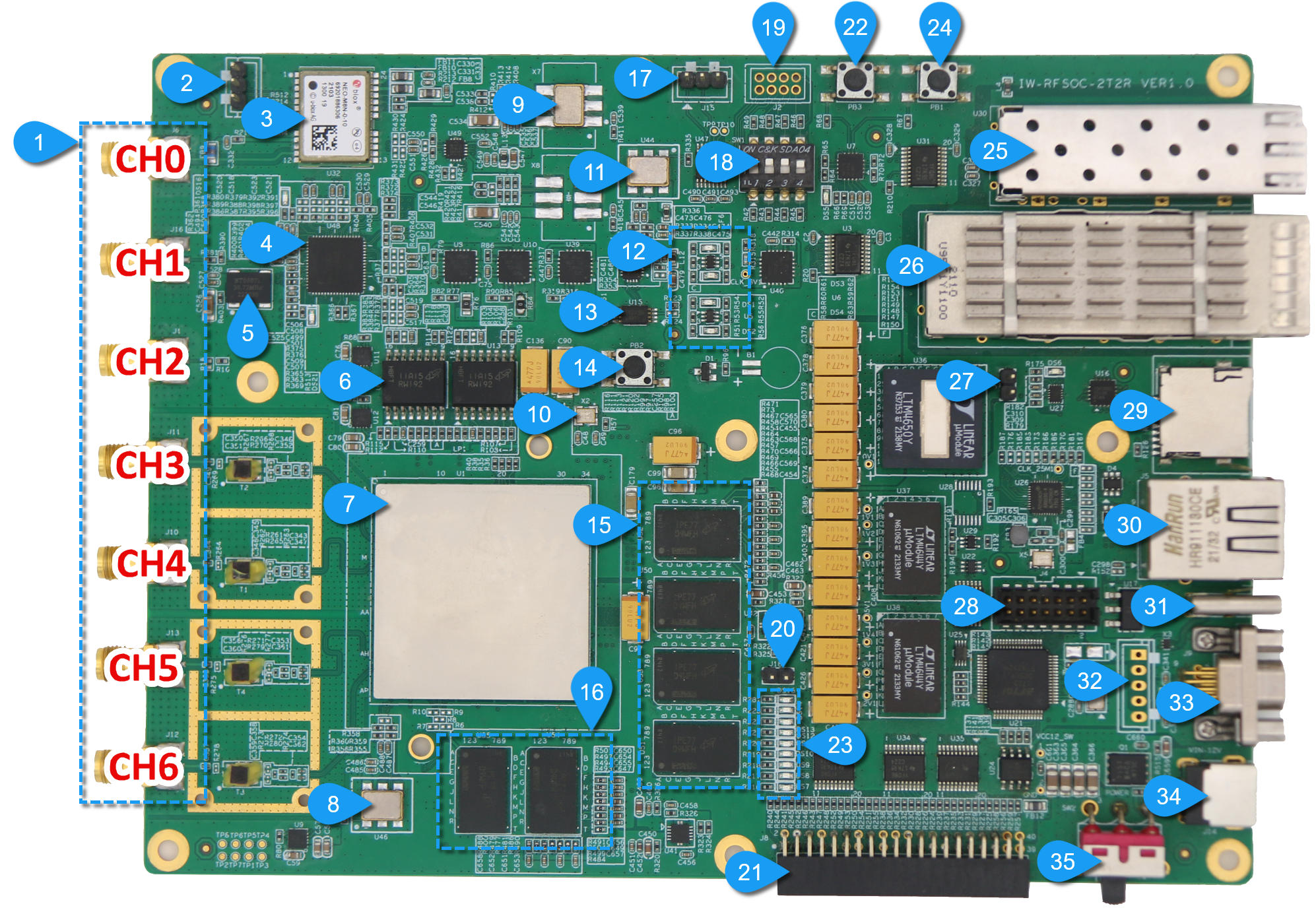

¶ 板卡整体结构

¶ 板卡部分功能及位置

| 编号 | 功能 |

|---|---|

| 1 | SMA 接口组,从上至下编号为 CH0-6。CH0 为 GPS 信号口;CH1 为外部参考时钟输入口;CH2 为 GPIO 口;CH3-6 为 RF-ADC/DAC 接口。 |

| 2 | GPS 模块的 USB 调试口,从上至下分别为 GND, DN,DP。 |

| 3 | GPS 模块。 |

| 4 | 时钟树芯片。 |

| 5 | 30.72MHz 晶振,用于为时钟树提供参考时钟。 |

| 6 | dual_parallel 模式的 QSPI nor Flash 芯片组,容量共 2Gbit (256MByte)。 |

| 7 | Xilinx Zynq UltraScale+ RFSoC XCZU27(47)DR-FFVE1156-2I 主芯片。 |

| 8 | 300MHz 晶振,用于为 PL 端内存提供参考时钟。 |

| 9 | 122.88MHz 晶振,用于为时钟树提供参考时钟。 |

| 10 | 33.33MHz 晶振,用于为 PS 端提供参考时钟。 |

| 11 | 156.25MHz 晶振,用于为 SFP+ 和 QSFP+ 接口提供参考时钟。 |

| 12 | FPGA 工作状态指示灯,从上至下依次为:PS_ERR_OUT,PS_ERR_STATUS,PS_INIT_B,PS_DONE。 |

| 13 | EEPROM,容量为 8Kbit (1KByte)。 |

| 14 | PL 端复位按钮。 |

| 15 | PS 端 DDR4 内存,最大 2400MT/s,64bit 位宽, 容量共 4GByte 。 |

| 16 | PL 端 DDR4 内存,最大 2666MT/s,32bit 位宽, 容量共 2GByte 。 |

| 17 | PL 端 UART 接口,从左到右分别为 TXD,RXD,GND。接口为 RS232 电平。 |

| 18 | 启动模式拨码开关。 |

| 19 | 启动模式排针预留接口。 |

| 20 | 5V 散热风扇供电接口,从左到右分别为 GND,5V。 |

| 21 | PL 端 GPIO 接口。 |

| 22 | PS 端复位按钮 |

| 23 | 电源指示灯及用户 LED[7:0] ,从上至下分别为 3.3V 电源指示,LED[7]-LED[0] 。 |

| 24 | 复位按钮。 |

| 25 | 10Gbps SFP+ 接口 |

| 26 | 40Gbps QSFP+ 接口 |

| 27 | 12V 散热风扇供电接口,从上到下分别为 GND,12V。 |

| 28 | JTAG 接口。 |

| 29 | Micro SD 卡座。 |

| 30 | RJ45接口,支持 10/100/1000M 三态以太网。 |

| 31 | USB Type-C 接口,支持 USB-JTAG 调试和 USB 转 UART。 |

| 32 | USB 接口插针,从上至下分别为 5V , DN , DP , ID , GND 。 |

| 33 | J30J 接口,支持 PL 端 SPI 和 PL 端 GPIO 接口。 |

| 34 | DC-044A 接口,12V 电源接口。 |

| 35 | 总电源开关,拨动至左侧为关,拨动至右侧为开。 |

表格中所有的方位(上、下、左、右)均指代如图中所示的相对位置,实际情况请根据板卡的实际摆放方式与图片对照使用。

¶ 启动模式

板卡可以通过拨码开关设置启动模式,板卡目前支持三种启动模式,见下表:

| 启动模式 | 拨码开关配置 | 启动模式码 [3:0] |

|---|---|---|

| PS JTAG | 4'b0000 | |

| QSPI Flash | 4'b0010 | |

| SD | 4'b0101 |

其余启动方式板卡暂不支持,如需获取详细信息可参阅Zynq UltraScale+ Device Technical Reference Manual (UG1085)。

¶ RF ADC/DAC 转换器

板卡共引出了两组 ADC 和 DAC ,并通过巴伦耦合电路将输入的单端信号转成了差分信号,将输出的差分信号转成了单端信号。

本板卡使用的巴伦器型号为TCM2-63WX+,并组合了阻抗匹配电路,其结构图如下:

由于巴伦器的限制,ADC和DAC可使用的频率范围为 30-6000MHz ;具体频率响应参数请参见TCM2-63WX+。

ADC 和 DAC 的 SMA 接口在编号 1 的位置处,其对应接口引脚见下表:

| 通道编号 | SMA接口编号 | 区块 | 通道 | 接口引脚 (P, N) |

|---|---|---|---|---|

| CH3 | J11 | DAC Tile 228 | DAC 2 | J2, J1 |

| CH4 | J10 | DAC Tile 228 | DAC 0 | N2, N1 |

| CH5 | J13 | ADC Tile 224 | ADC 1 | AH2, AH1 |

| CH6 | J12 | ADC Tile 224 | ADC 0 | AK2, AK1 |

需要RF通道正常工作,还需提供参考时钟和SYSREF信号,板卡将信号输入到了如下引脚:

| 接口名称 | 接口引脚 (P, N) |

|---|---|

| ADC_REFCLK | AD5, AD4 |

| DAC_REFCLK | L5, L4 |

| SYSREF | N5, N4 |

参考时钟和SYSREF可以由用户自行配置来改变采样频率,然而两者之间还具有一定关系,具体信息可以参阅Zynq UltraScale+ RFSoC RF Data Converter v2.6 Gen 1/2/3/DFE LogiCORE IP Product Guide (PG269)。

¶ DDR4内存

¶ PS端DDR4内存

PS 端 DDR4 内存采用了 4 颗美光 MT40A512M16LY-062E IT:E 内存,组成了 4GB 的内存,其配置如下表:

| BG地址宽度 | BA地址宽度 | 行地址宽度 | 列地址宽度 | 页大小 | 颗粒配置 | 数据位宽 |

|---|---|---|---|---|---|---|

| 1 | 2 | 16 | 10 | 2KB | 512Mx16 | 64bit |

内存时序参数:

| CLK | Period | CL | RCD | RP | CWL | tRC | tRAS | tFAW |

|---|---|---|---|---|---|---|---|---|

| 1200MHz | 833ps | 17 | 17 | 17 | 12 | 45.75ns | 32ns | 30ns |

虽然内存颗粒支持高达 3200MT/s 的传输速率,然而 PS 端最高支持 2400MT/s 的传输速率,具体请参考Zynq UltraScale+ RFSoC Data Sheet: DC and AC Switching Characteristics (DS926)。

此处展示的是内存与主芯片适配的性能最高参数(同时也意味着功耗最高),用户可根据自己使用场景进行调整以平衡功耗和性能。

¶ PL端DDR4内存

PS 端 DDR4 内存采用了 2 颗美光 MT40A512M16LY-062E IT:E 内存,组成了 2GB 的内存,并使用 300M 差分晶振作为参考时钟,其配置如下表:

| BG地址宽度 | BA地址宽度 | 行地址宽度 | 列地址宽度 | 页大小 | 颗粒配置 | 数据位宽 |

|---|---|---|---|---|---|---|

| 1 | 2 | 16 | 10 | 2KB | 512Mx16 | 32bit |

该内存时序参数:

| CLK | Period | CL | RCD | RP | CWL | tRC | tRAS | tFAW |

|---|---|---|---|---|---|---|---|---|

| 1333MHz | 750ps | 19 | 19 | 19 | 14 | 45.75ns | 32ns | 30ns |

虽然内存颗粒支持高达 3200MT/s 的传输速率,然而 PS 端最高支持 2666MT/s 的传输速率,具体请参考Zynq UltraScale+ RFSoC Data Sheet: DC and AC Switching Characteristics (DS926)。

此处展示的是内存与主芯片适配的性能最高参数(同时也意味着功耗最高),用户可根据自己使用场景进行调整以平衡功耗和性能。

PL 端使用了300M 的差分晶振为 DDR4 内存提供参考时钟,时钟与内存引脚定义:

| 内存引脚 | 接口引脚 (S) | 内存引脚 | 接口引脚 (S) (T, C) |

|---|---|---|---|

| DQ[0] | AE14 | A[0] | AG12 |

| DQ[1] | AD16 | A[1] | AJ11 |

| DQ[2] | AE15 | A[2] | AH10 |

| DQ[3] | AC17 | A[3] | AH9 |

| DQ[4] | AD15 | A[4] | AG10 |

| DQ[5] | AE18 | A[5] | AG9 |

| DQ[6] | AE13 | A[6] | AM11 |

| DQ[7] | AD18 | A[7] | AG11 |

| DQ[8] | AF13 | A[8] | AE11 |

| DQ[9] | AG17 | A[9] | AF10 |

| DQ[10] | AE16 | A[10] | AM12 |

| DQ[11] | AH17 | A[11] | AF12 |

| DQ[12] | AF14 | A[12] | AL12 |

| DQ[13] | AF17 | A[13] | AF11 |

| DQ[14] | AF16 | A[14] | AN12 |

| DQ[15] | AF18 | A[15] | AL11 |

| DQ[16] | AK15 | A[16] | AL13 |

| DQ[17] | AK18 | BA[0] | AK9 |

| DQ[18] | AK16 | BA[1] | AK10 |

| DQ[19] | AJ15 | BG[0] | AP12 |

| DQ[20] | AK14 | DM[0] | AC13 |

| DQ[21] | AL18 | DM[1] | AG15 |

| DQ[22] | AJ16 | DM[2] | AH13 |

| DQ[23] | AJ17 | DM[3] | AM14 |

| DQ[24] | AN17 | DQS[0] | AC16, AC15 |

| DQ[25] | AN18 | DQS[1] | AG14, AH14 |

| DQ[26] | AP16 | DQS[2] | AH18, AJ18 |

| DQ[27] | AP17 | DQS[3] | AL17, AM16 |

| DQ[28] | AP15 | CK | AJ10, AJ9 |

| DQ[29] | AM17 | CKE | AN13 |

| DQ[30] | AM15 | ACT_N | AN8 |

| DQ[31] | AN15 | ODT | AK13 |

| CS_N | AP13 | RESET_N | AN7 |

| CLK_REF | AL9, AM9 |

¶ 以太网接口

¶ PS端10/100/1000M三态接口

板卡使用一片高通 AR8035-AL1A 10/100/1000M 三态以太网 PHY 芯片通过 RGMII 与 PS 端相连。

具体接口定义如下:

| 接口名称 | 接口模块 | 接口引脚 |

|---|---|---|

| RGMII | GEM 3 | MIO 64 .. 75 |

| MDIO | MDIO 3 | MIO 76 .. 77 |

| RESETN | GPIO 2 | MIO 60 |

本板卡采用的芯片所需要的配置与 Xilinx 公司官方推荐配置有所差异,在使用官方自带的 Lwip 例程时需要进行额外配置,具体请参阅二次开发建议

¶ PL端10G SFP+接口

板卡在芯片的 PL 端接入了一个支持高达 10Gbps 的 SFP+ 接口,可用于接入 10G 以太网。需要注意的是,虽然其数据接口接入了 PL 端的 GTY 收发器,但其控制信号接入了 PS 端,这样做符合大部分使用场景的需求和习惯。

板卡使用了一个时钟缓冲器芯片为 GTY 提供参考时钟,可以通过芯片选择使用 156.25MHz 晶振或可编程时钟,这为接口参考时钟的选择提供了很大的灵活性,默认情况下使用的是 156.25MHz 晶振,具体操作方法请参见时钟树及配置

其接口定义如下:

| 接口名称 | 接口模块 | 接口引脚 (S) (P, N) |

|---|---|---|

| CLK_REF | GTY Quad X0Y2, Bank 129, REFCLK_0 | H28, H29 |

| RX | GTY Quad X0Y2, Bank 129, CHANNEL_X0Y8 | F33, F34 |

| TX | GTY Quad X0Y2, Bank 129, CHANNEL_X0Y8 | E30, E31 |

| TX_DISABLE | GPIO 0 | MIO 20 |

| LOS | GPIO 0 | MIO 21 |

| SDA | IIC 0 | MIO 22 |

| SCL | IIC 0 | MIO 23 |

| MOD_DEF0 | GPIO 0 | MIO 24 |

| TX_FAULT | GPIO 0 | MIO 25 |

¶ PL端40G QSFP+接口

板卡在芯片的 PL 端接入了一个支持高达 40Gbps 的 QSFP+ 接口,可用于接入 40G 以太网。同样的,数据接口接入了 PL 端的 GTY 收发器,但其控制信号接入了 PS 端。

板卡使用了一个时钟缓冲器芯片为 GTY 提供参考时钟,可以通过芯片选择使用 156.25MHz 晶振或可编程时钟,默认情况下使用的是 156.25MHz 晶振,具体操作方法请参见时钟树及配置

其接口定义如下:

| 接口名称 | 接口模块 | 接口引脚 (S) (P, N) |

|---|---|---|

| CLK_REF | GTY Quad X0Y1, Bank 128, REFCLK_0 | M28, M29 |

| RX0 | GTY Quad X0Y1, Bank 128, CHANNEL_X0Y4 | P33, P34 |

| RX1 | GTY Quad X0Y1, Bank 128, CHANNEL_X0Y5 | M33, M34 |

| RX2 | GTY Quad X0Y1, Bank 128, CHANNEL_X0Y6 | K33, K34 |

| RX3 | GTY Quad X0Y1, Bank 128, CHANNEL_X0Y7 | H33, H34 |

| TX0 | GTY Quad X0Y1, Bank 128, CHANNEL_X0Y4 | N30, N31 |

| TX1 | GTY Quad X0Y1, Bank 128, CHANNEL_X0Y5 | L30, L31 |

| TX2 | GTY Quad X0Y1, Bank 128, CHANNEL_X0Y6 | J30, J31 |

| TX3 | GTY Quad X0Y1, Bank 128, CHANNEL_X0Y7 | G30, G31 |

| SCL | IIC 0 | MIO 30 |

| SDA | IIC 0 | MIO 31 |

| LPMODE | GPIO 1 | MIO 35 |

| INTL | GPIO 1 | MIO 36 |

| MODPRSL | GPIO 1 | MIO 37 |

| RESETL | GPIO 1 | MIO 38 |

| MODSELL | GPIO 1 | MIO 39 |

¶ 存储器配置

¶ PS端Micro SD

PS 端接入了一个 Micro SD 卡槽至 PS 端的 SD1 控制器,可用于存储用户的程序和配置文件,其配置及引脚定义为:

| 参数 | 配置 |

|---|---|

| Interface | SD 1 |

| Slot Type | SD 2.0 |

| IO Port | MIO 46 .. 51 |

| Data Transfer Mode | 4bit |

| CD | MIO 45 |

¶ PS端QSPI nor Flash

板卡在 PS 端接入了两片 MT25QU01GBBB8ESF-0SIT QSPI 芯片,提供了最大 2x1Gbit = 256MB 的容量,可用于存储 FPGA 的 bit 文件、程序和配置文件。两片 QSPI 芯片是通过并行的方式接入 PS 端,其工作方式可以参考Zynq UltraScale+ Device Technical Reference Manual (UG1085)。

只有将接口模式调整为 QSPIx8-dual_parallel 模式才能使用两片芯片的最大容量并达到最大启动加载速度。

其配置及引脚定义为:

| 参数 | 配置 |

|---|---|

| Interface | Dual Parallel |

| QSPI Data Mode | x4 |

| IO Port | MIO 0 .. 12 |

¶ PL端EEPROM

PL 端接入了一个 8 Kbit (1 Kbyte) 容量的 EEPROM 芯片,使用 IIC 总线接入,型号为:M24C08-RDW6TP用于存储用户的配置文件,其定义为:

| 接口名称 | 接口引脚 (S) |

|---|---|

| SDA | C11 |

| SCL | B10 |

| E2 | Vcc |

由于板卡上将该芯片的地址配置引脚 E2 上拉,因此该芯片的 IIC 地址为:

| b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

|---|---|---|---|---|---|---|---|

| 1 | 0 | 1 | 0 | 1 | A[9] | A[8] | RW |

其中 RW 为读写控制 bit ,1 为读取,0 为写入。A[9] 和 A[8] 与传输的第二个 Byte 的 A[7:0] 共同组成了一个 10bit 的地址空间,每个地址对应 EEPROM 中的一个 Byte 数据。

该芯片虽然工作模式类似 IIC 总线的 10bit 地址模式,然而两者并不相同。 IIC 的 10bit 地址模式 b[7:3] 为 '11110' ,而该芯片为 '1010x'。

¶ 扩展接口

¶ PL端UART接口

PL 端共连接了两个 UART 接口,分别为 PL-UART0 和 PL-UART1 ,其中 PL-UART0 连接至 USB-JTAG 调试接口上(关于 USB-JTAG 的详细信息请参阅调试接口部分),PL-UART1 连接至座子,座子的位置在编号 17 处。

PL-UART0 接口的定义请参照 USB-JTAG 和 UART ,这里提供编号 17 座子的定义和引脚:

| 引脚号 | 接口名称 | 接口引脚 (S) |

|---|---|---|

| 1 | TXD | C10 |

| 2 | RXD | C9 |

| 3 | GND | GND |

编号 17 座子输入和输出电平经过了 MAX3232 芯片转换,采用的是 RS232 标准电平,非 TTL 或 CMOS 电平。请连接正确电平的总线,以免对板卡或您的设备造成损坏!

¶ PL端SPI接口

PL 端引出了一个 SPI 接口,连接至 J30J 接口,接口的位置在编号 33 处,具体定义为:

| 引脚号 | 接口名称 | 接口引脚 (S) |

|---|---|---|

| 1 | PWR | 3.3V |

| 2 | PWR | 3.3V |

| 3 | GPIO | J11 |

| 4 | GND | GND |

| 5 | GND | GND |

| 6 | CLK | F10 |

| 7 | CS | H11 |

| 8 | MISO | E11 |

| 9 | MOSI | D11 |

¶ PL端GPIO接口

PL 端提供了三组 GPIO 接口,第一组是位于编号 1 CH2 处的 SMA GPIO,其定义为:

| 引脚号 | 接口名称 | 接口引脚 (S) |

|---|---|---|

| 1 | GPIO | K11 |

第三组位于编号 21 处,其定义为:

| 引脚号 | 接口名称 | 接口引脚 (S) | 引脚号 | 接口名称 | 接口引脚 (S) |

|---|---|---|---|---|---|

| 1 | GPIO | J13 | 2 | GPIO | H14 |

| 3 | GPIO | K14 | 4 | GPIO | K15 |

| 5 | GPIO | J14 | 6 | GPIO | F13 |

| 7 | GPIO | H15 | 8 | GPIO | F14 |

| 9 | GPIO | E14 | 10 | GPIO | K12 |

| 11 | GPIO | D13 | 12 | GPIO | A13 |

| 13 | GPIO | A14 | 14 | GPIO | J12 |

| 15 | GPIO | F12 | 16 | GPIO | G12 |

| 17 | GPIO | AH12 | 18 | GPIO | AP2 |

| 19 | GPIO | AJ12 | 20 | GPIO | AP3 |

| 21 | GPIO | AN1 | 22 | GPIO | AN4 |

| 23 | GPIO | AN2 | 24 | GPIO | AM5 |

| 25 | GPIO | AD17 | 26 | GPIO | AL16 |

| 27 | GPIO | AD13 | 28 | GPIO | AJ13 |

| 29 | GPIO | AG16 | 30 | GPIO | AN14 |

| 31 | GPIO | AH15 | 32 | GPIO | AP8 |

| 33 | GPIO | K10 | 34 | GPIO | H10 |

| 35 | GPIO | H9 | 36 | GPIO | F9 |

| 37 | GND | GND | 38 | PWR | 3.3V |

| 39 | GND | GND | 40 | PWR | 3.3V |

由于该接口上的 GPIO 来自不同 bank ,并且经过电平转换的状态各不相同,因此在针对该接口进行二次开发前,我们强烈建议您先阅读GPIO扩展卡开发建议内容。

¶ 调试接口

¶ USB-JTAG和UART

板卡上板载了一片 FT4232HL 芯片作为 USB-JTAG 控制器,可以通过连接编号 31 处的 USB Type-C 接口至 PC 端来使用,或者连接编号 32 处的排针接口至 PC 端使用。

在使用 USB-JTAG 前,请先确保正确安装了 FT4232HL 芯片驱动。

除了 JTAG 接口外,芯片还接出了两个 UART 接口分别连接在 PS 端和 PL 端用于调试,其中 PS-UART0 定义如下:

| 参数 | 配置 |

|---|---|

| Interface | UART 0 |

| IO Port | MIO 18 .. 19 |

PL-UART0 定义如下:

| 接口名称 | 接口引脚 (S) |

|---|---|

| TXD | C14 |

| RXD | D14 |

| CTS | B13 |

| RTS | C13 |

¶ JTAG 接口

当 USB-JTAG 不可用或不稳定时,可以使用 JTAG 接口直接对板卡进行调试, JTAG 接口位于编号 28 处,其定义为:

| 引脚号 | 接口名称 | 引脚号 | 接口名称 |

|---|---|---|---|

| 1 | GND | 2 | VREF |

| 3 | GND | 4 | TMS |

| 5 | GND | 6 | TCK |

| 7 | GND | 8 | TDO |

| 9 | GND | 10 | TDI |

| 11 | GND | 12 | NC |

| 13 | GND | 14 | RESETN |

¶ LED

¶ 状态指示灯

状态指示灯位于编号 12 处,其具体信号为:

| LED编号 | 信号名称 | 功能 |

|---|---|---|

| 1 | PS_ERR_OUT | 因意外断电、 PMU 错误导致 CSU 复位或触发 PMU 中的异常而导致的 PS 错误。 |

| 2 | PS_ERR_STATUS | PS 处于锁定状态,或 PMU 固件中的错误指示。 |

| 3 | PS_INIT_B | FPGA 初始化。 |

| 4 | PS_DONE | FPGA 初始化成功。 |

关于 FPGA 状态信号的详细内容可以参阅 Zynq UltraScale+ Device Technical Reference Manual (UG1085)。

¶ 用户可编程LED

用户可编程 LED 采用上拉点亮模式,即输出高电平点亮 LED 。这组 LED 位于编号 23 处,其具体信号为:

| LED编号 | 接口引脚 (S) |

|---|---|

| 7 | AP5 |

| 6 | AN5 |

| 5 | AP6 |

| 4 | AM6 |

| 3 | AP7 |

| 2 | AM7 |

| 1 | AM8 |

| 0 | AN9 |

¶ GPS模块

板卡板载了一块 GPS 模块,型号为 NEO-M8n-0-10 。该模块通过 UART 与 PL 端相连,并为 PL 端提供秒脉冲。其接收天线通过 SMA 口与板卡相连,SMA 口的位置为编号 1 CH0 处,其接口定义为:

| 接口名称 | 接口引脚 (S) |

|---|---|

| TXD | D9 |

| RXD | A9 |

| 1PPS | E9 |

| RESETN | G10 |

为了更好的接收 GPS 信号,可以将 GPS 天线置于室外。

¶ 按钮

¶ 复位按钮

位置为编号 24 处的按钮控制 FPGA 芯片整体复位,其控制信号为 PS_POR_B。

为了使信号满足复位时序,该按钮被接入了时序控制芯片,因此复位存在延时。

关于复位系统的更多信息,请参阅 Zynq UltraScale+ Device Technical Reference Manual (UG1085) 。

¶ PS端复位按钮

位置为编号 22 处的按钮控制 PS 端复位,其控制信号为 PS_SRST_B。

为了使信号满足复位时序,该按钮被接入了时序控制芯片,因此复位存在延时。

关于复位系统的更多信息,请参阅 Zynq UltraScale+ Device Technical Reference Manual (UG1085) 。

¶ PL端复位按钮

位置为编号 14 处的按钮控制 PL 端复位,其控制信号为 PS_PROG_B。

关于复位系统的更多信息,请参阅 Zynq UltraScale+ Device Technical Reference Manual (UG1085) 。

¶ 时钟

¶ PS端参考时钟

PS 端接入了一个 33.33MHz 的晶振作为参考时钟。

¶ PS端RTC时钟

PS 端的 RTC 模块接入了一个 32.768KHz 的晶振作为参考时钟。

关于 RTC 的更多信息,请参阅 Zynq UltraScale+ Device Technical Reference Manual (UG1085) 。

¶ 时钟树及配置

板卡使用了一个时钟树芯片 LMK04828 为 FPGA 的多个工作部分进行时钟分发,这里将详细给出时钟树的连接方式。

从图中展示了 LMK04828 时钟数芯片以及其外围主要时钟的连接状态,板卡使用了 LMK04828 推荐的双锁相环模式。芯片 CLKin1 引脚连接的是位于编号 1 CH1 位置的 SMA 外部输入参考时钟口,而 CLKin2 连接了一个频率为 30.72MHz 的晶振。在芯片的 OSCin 引脚上,有两个压控振荡器通过时钟选通芯片 MUX1 输入进来。在默认情况下, MUX1 选通的是 122.88MHz 的压控振荡器,并且 48MHz 晶振位置不安装器件。这里采用的压控振荡器型号为 V9P3CL150WXA-122.88MHz。

芯片主要为 FPGA 上的 RF-ADC/DAC 以及其相关的模块提供参考时钟,同时也兼顾了给 GTY 模块提供参考时钟(默认不启用)。在默认情况下, MUX2 选通的是 156.25MHz 的晶振。时钟数为 FPGA 提供时钟的引脚为:

| 接口名称 | 接口引脚 (P, N) |

|---|---|

| ADC_REFCLK | AD5, AD4 |

| PL_REFCLK | AP11, AP10 |

| PL_SYSREF | AM10, AN10 |

| DAC_REFCLK | L5, L4 |

| SYSREF | N5, N4 |

| QSFP_REFCLK | M28, M29 |

| SFP_REFCLK | H28, H29 |

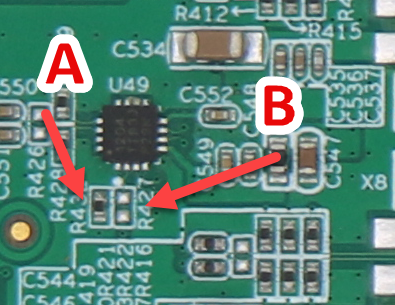

两个时钟选路器均采用了 CDCLVP1204 芯片,其选路引脚由电阻安装位置决定,对于 MUX1 来说,其位置如下图所示:

默认 MUX1 的电阻状态如图所示,其中电阻位于 A 位置选通 122.88MHz 压控振荡器,位于 B 位置选通 48MHz 压控振荡器。

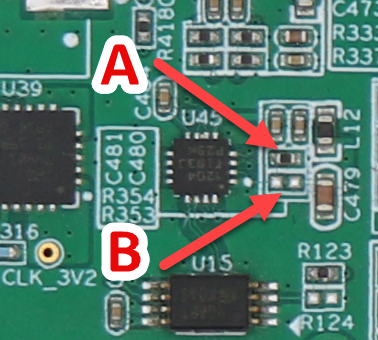

对于 MUX2 来说,其位置如下图所示:

默认 MUX2 的电阻状态如图所示,其中电阻位于 A 位置选通 156.25MHz 晶振,位于 B 位置选通 LMK04828 芯片。

LMK04828 通过 SPI 总线与 PL 端相连,其与 PL 端相连的所有控制接口定义如下:

| 接口名称 | 接口引脚 (S) |

|---|---|

| SDIO | B11 |

| SCK | G11 |

| CS | A10 |

| SYNC | A12 |

| RESET | B12 |

| CLKIN_SEL0 | E12 |

| CLKIN_SEL1 | D12 |

| STATUS_LD1 | G13 |

| STATUS_LD2 | H13 |

关于时钟树配置的方法和建议请参见时钟树配置建议

¶ 电源

板卡通过一个 DC-044A 接口为整板供电,电源输入电压应为 12V 直流,电流不应小于 5A 。板卡为 FPGA 核心提供了 0.85V@50A 的充沛供电,同时对不同的 IO Bank 也采用了不同的 IO 电压,详细见下表:

当芯片的逻辑设计功耗较高时,请确保充足的散热冗余,否则可能损坏板卡。具体建议请参阅散热建议。

| IO Bank | 电压 |

|---|---|

| PL BANK 65 | 1.2V |

| PL BANK 66 | 1.2V |

| PL BANK 88 | 3.3V |

| PL BANK 89 | 3.3V |

| PS BANK 500 | 1.8V |

| PS BANK 501 | 1.8V |

| PS BANK 502 | 1.8V |

| PS BANK 503 | 1.8V |

| PS BANK 504 | 1.2V |

PS BANK 502 连接着以太网 PHY 芯片,因此支持多种电平模式,板卡默认为 1.8V ,也可通过修改配置电阻修改为 3.3V 。